2021. 2. 25. 22:50ㆍComputer(인강)/운영체제

안녕하세요 bannavi입니다^ㅅ^

오늘은 다중 단계 페이징 시스템과 페이징 시스템 장점에 대해 살펴볼거에요

바로 시작하겠습니다^ㅅ^

다중 단계 페이징 시스템

* 32bit 시스템에서 4KB 페이지를 위한 페이징 시스템은

- 하위 12bit는 오프셋

- 상위 20bit가 페이징 번호이므로, 2의 20승(1048576)개의 페이지 정보가 필요함

* 페이징 정보를 단계를 나누어 생성

- 필요없는 페이지는 생성하지 않으면, 공간 절약 가능

페이지 번호를 나타내는 bit를 구분해서, 단계를 나눔(리눅스는 3단계, 최근 4단계)

해당 페이지 번호를 찾아서

그 페이지 번호와 OFFSET정보를 가지고

물리주소에 정보(데이터)를 가지고 온다

MMU와 TLB(컴퓨터 구조)

MMU가 물리 주소를 확인하기 위해 메모리를 갔다와야 함

1~5의 과정을 거칠텐데 문제는, 메모리에 왔다갔다 하는 시간도 많이걸리겠죠.

그래서 요것을 해결하기 위해서 별도의 캐시보조하드웨어를 갖다 놓습니다.

TLB(Translation Lookaside Buffer): 페이지 정보 캐쉬

이렇게만 보니 잘 모르겠죠.

요렇게 말입니다!!!!!

1번에서 A라는 가상주소를 입력했더니 물리주소가A'가 나왔다라고 했을때,

이 물리주소 정보를 TLB에 저장하는겁니다.

그 다음번부터는 만일 A라는 가상 메모리 주소를 요청하면

페이지 테이블까지 다녀오는것이 아니라, MMU단계에서 TLB를 한번 찾아봅니다.

A라는 주소에 물리주소가 있는지 말이죠.

만약에 물리주소가 있으면?!

2번, 3번 작업을 하지 않고 TLB에 있던 물리주소로 메모리에 접근할 수 있기 떄문에

이렇게 접근하는 과정이 확 단축되겠죠?! 최소 2번에서 한번은요!

정리해보면

TLB는 최근 물리주소로 변환된 가상주소 정보를 저장하는 장치라고 한다는 것입니다.

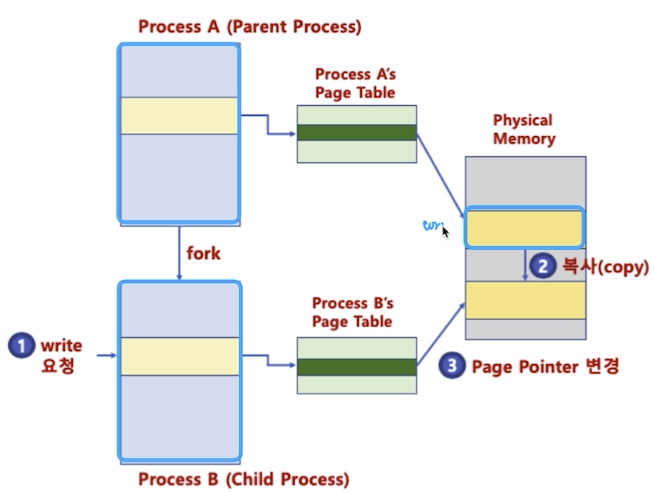

페이징 시스템과 공유 메모리

- 프로세스간 동일한 물리 주소를 가리킬 수 있음(공간 절약, 메모리 할당 시간 절약)

- 물리 주소 데이터 변경시

* 물리 주소에 데이터 수정 시도시, 물리 주소를 복사할 수 있음(copy-on-write)

'Computer(인강) > 운영체제' 카테고리의 다른 글

| 페이지 교체 알고리즘 (0) | 2021.02.25 |

|---|---|

| 페이지 폴트 (0) | 2021.02.25 |

| 페이징 시스템 (0) | 2021.02.25 |

| 가상 메모리 개념 (0) | 2021.02.25 |

| deadlock과 starvation (0) | 2021.02.25 |